## THE UNIVERSITY OF CHICAGO

# UNDERSTANDING NETWORK COMMUNICATION REQUIREMENTS FOR THE $\mbox{UPDOWN SYSTEM}$

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCE IN CANDIDACY FOR THE DEGREE OF MASTER OF SCIENCE

DEPARTMENT OF COMPUTER SCIENCE

BY JIYA SU

CHICAGO, ILLINOIS GRADUATION DATE

Copyright  $\bigcirc$  2025 by Jiya Su All Rights Reserved

# TABLE OF CONTENTS

| LIS | ST O | F FIGURES                                          |

|-----|------|----------------------------------------------------|

| LIS | ST O | F TABLES vii                                       |

| ΑE  | BSTR | ACT ix                                             |

| 1   | INT  | RODUCTION                                          |

| 2   | BAC  | CKGROUND                                           |

|     |      | I/O Channel Bandwidth and Emerging Technologies    |

|     |      | 2.1.1 Co-Packaged Optics (CPO)                     |

|     | 2.2  | Network Packet Format                              |

|     |      | 2.2.1 Ethernet Packet Format                       |

|     |      | 2.2.2 HPE Slingshot Packet Format                  |

|     |      | 2.2.3 NVLink Packet Format                         |

|     | 2.3  | Packet Frame Forwarding Rate                       |

|     |      | 2.3.1 HPE Slingshot CASSINI NIC and Rosetta Switch |

|     |      | 2.3.2 NVLink4 and NVLink4 Switch                   |

|     |      | 2.3.3 51.2T TH5-Bailly                             |

|     |      | 2.3.4 Other HPC Interconnect technologies          |

|     | 2.4  | Large-scale systems                                |

|     |      | 2.4.1 One Node Configuration                       |

|     |      | 2.4.2 Whole Machine System Comparison              |

| 3   | UPI  | OOWN SYSTEM                                        |

|     | 3.1  | UpDown Architecture                                |

|     | 3.2  | UpDown System         22                           |

|     | 3.3  | UpDown System Network Design                       |

|     |      | 3.3.1 Network Packet Size                          |

|     | 3.4  | UDKVMSR                                            |

|     | 3.5  | UpDown Simulator                                   |

| 4   | SYS  | TEM NETWORK TRAFFIC CHARACTERISTIC                 |

|     | 4.1  | Summary of Network Traffic Characteristic          |

|     | 4.2  | System-level workload                              |

|     |      | 4.2.1 Input Dataset Characteristics                |

|     |      | 4.2.2 Application Characteristics                  |

|     | 4.3  | Communication Pattern Analysis                     |

|     |      | 4.3.1 Point-to-Point Traffic                       |

|     |      | 4.3.2 Bisection Analysis                           |

|     | 4.4  | Network Packet Size                                |

|     | 4.5  | Network Injection Bandwidth Per Node               |

|     | 4.5.1 Average Injection Bandwidth                         |

|-----|-----------------------------------------------------------|

|     | 4.5.2 Instantaneous Injection Bandwidth                   |

| 4   | .6 Network Packet Injection Rate Per Node                 |

|     | 4.6.1 Average Packet Injection Rate                       |

|     | 4.6.2 Instantaneous Packet Injection Rate                 |

| 4   | .7 Other Characteristics                                  |

| 4   | .8 Conclusion                                             |

|     | UNDERSTANDING UPDOWN ARCHITECTURE AND APPLICATION PERFOR- |

| N   | MANCE SENSITIVITY TO NETWORK PERFORMANCE                  |

| 5   | .1 Methodology                                            |

| 5   | .2 Network Latency Sensitivity                            |

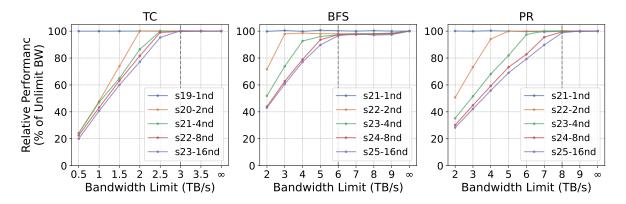

| 5   | .3 Network Injection Bandwidth Sensitivity                |

|     | 5.3.1 Influence of Sharp Peak Instantaneous Bandwidth     |

|     | 5.3.2 Injection Bandwidth Estimation over Time            |

| 5   | .4 Conclusion                                             |

| 6 F | PROJECTION TO FULL-SCALE UPDOWN SYSTEM                    |

| 6   | .1 Projection Methodology                                 |

|     | 6.1.1 Input Graph Size                                    |

|     | 6.1.2 Network Traffic                                     |

|     | 6.1.3 Execution Time                                      |

| 6   | .2 Result and Analysis                                    |

|     | 6.2.1 Without Injection Bandwidth Limitation              |

|     | 6.2.2 With Injection Bandwidth Limitation                 |

| 7 S | UMMARY AND FUTURE WORK                                    |

| 7   | .1 Summary                                                |

| 7   | .2 Future Work                                            |

| DEE | FDFNCFC                                                   |

# LIST OF FIGURES

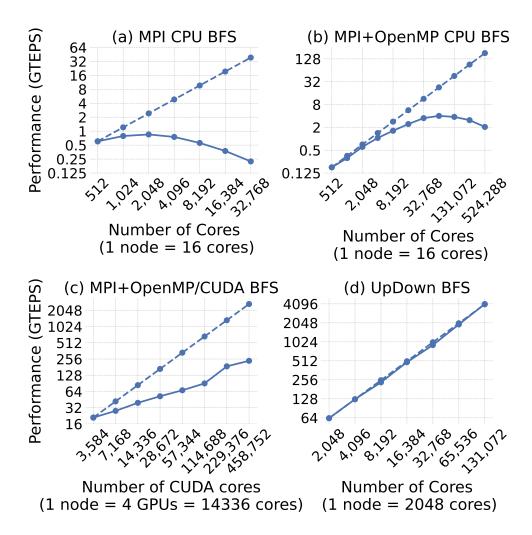

| 1.1                                                                                 | The solid line is the real performance, and the dashed line is the linear performance. (a) and (b): Weak scaling performance results using RMAT graphs of scale 25 to 35 on the Blue Gene/Q system. The MPI-CPU configuration utilizes 16 processes per node, while the hybrid configuration (MPI+OpenMP) employs 1 process per node and 16 threads per node [Adapted from [1]]. (c) Weak scaling performance with scale 26 RMAT graphs on each Tesla P100 GPU up to 124 GPUs on an early access system (Ray) of LLNL's upcoming CORAL/Sierra supercomputer [Adapted from [2]]. (d) Weak scaling performance using RMAT graphs of scale 22 to 28 on the UpDown system                                                                                                                                                                                                    | 2                                                              |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

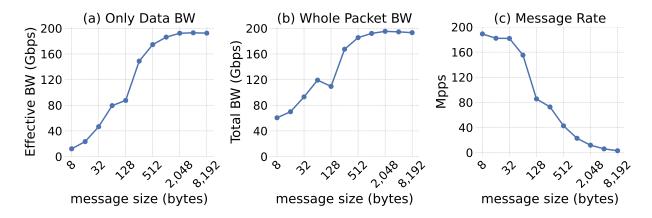

| 2.1 2.2                                                                             | Remote memory access bandwidth and message rate as a function of data payload size in message for 64 processes per NIC on the Shadow system. [Adapted from [3]]. Message rate vs. message size for various high-speed interconnect technologies as of 2019. [Adapted from [3]]. HPC Ethernet refers to enhanced Ethernet (e.g., Slingshot) optimized for HPC with adaptive routing and low-latency transport. HDR InfiniBand delivers 200 Gbps using PAM4 signaling and low-latency RDMA, suitable for modern HPC and AI workloads. EDR InfiniBand provides 100 Gbps using NRZ, widely adopted in earlier HPC systems. Aries is Cray's proprietary interconnect, utilizing a Dragonfly topology with adaptive routing for low-latency communication. RoCEv1 enables RDMA over Layer 2 Ethernet, requiring a lossless fabric and typically constrained to a single subnet | 11                                                             |

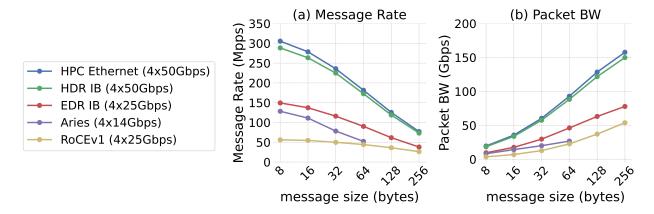

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                     | UpDown Node has 1 CPU, 32 UpDown accelerators with uniform access to 8 HBM stacks. Each UpDown accelerator has 64 event-driven programmable lanes. Event Driven Execution on UpDown lane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19<br>20<br>22<br>23<br>24                                     |

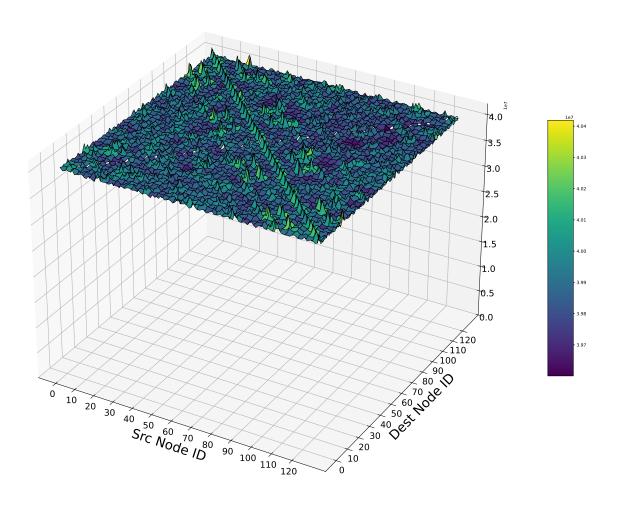

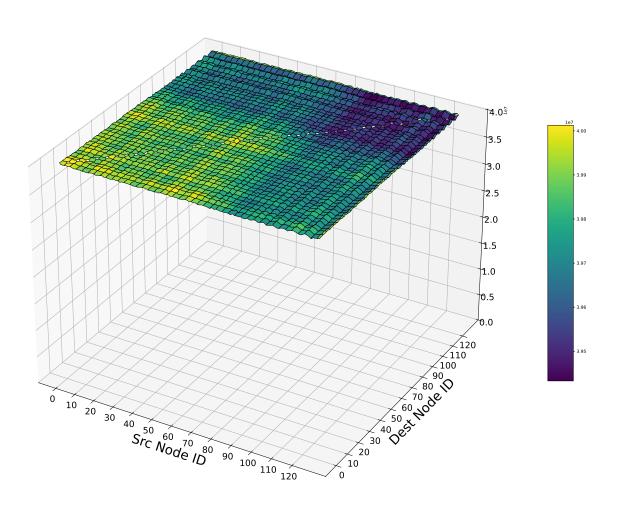

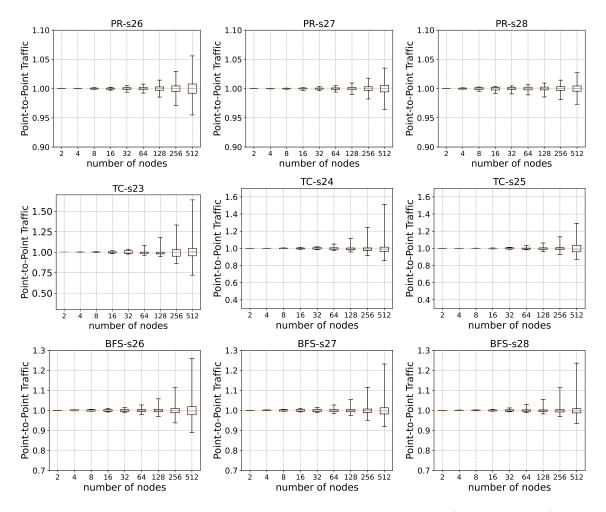

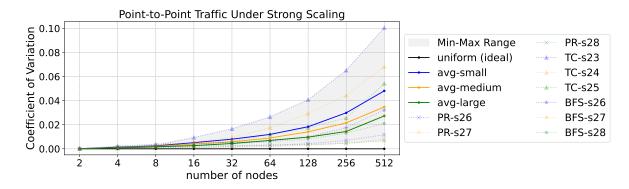

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | ( 0 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30<br>31<br>33<br>33<br>35<br>36<br>37<br>38<br>39<br>41<br>42 |

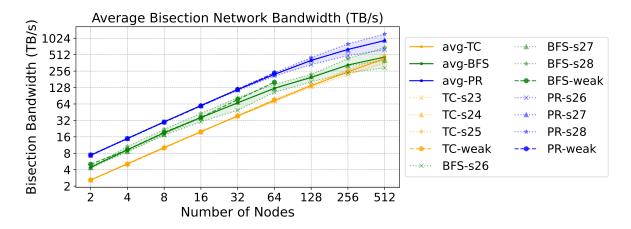

| 4.13       | Application Use of Bisection Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.14       | Average network packet size on 2-512 nodes under strong and weak Scaling                                                                                                                                                                                                                                                                                                                                                                                                                            | 43             |

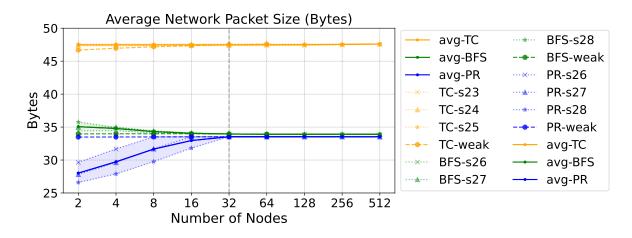

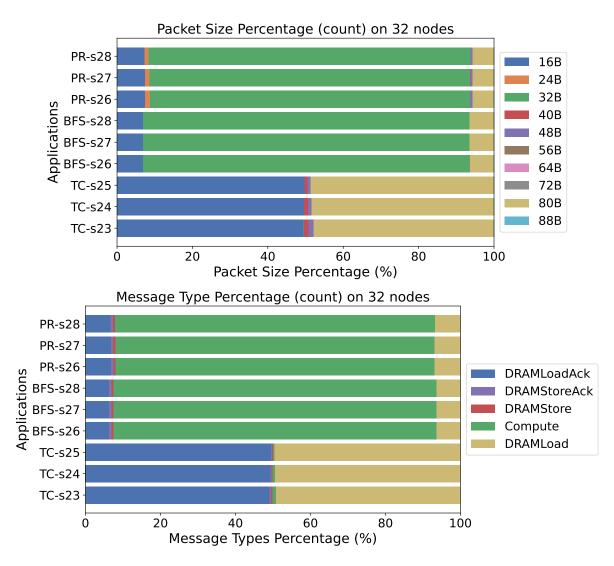

| 4.15       | Distribution of network packet sizes (upper) and packet type ratios (lower) at 4 nodes                                                                                                                                                                                                                                                                                                                                                                                                              | 4              |

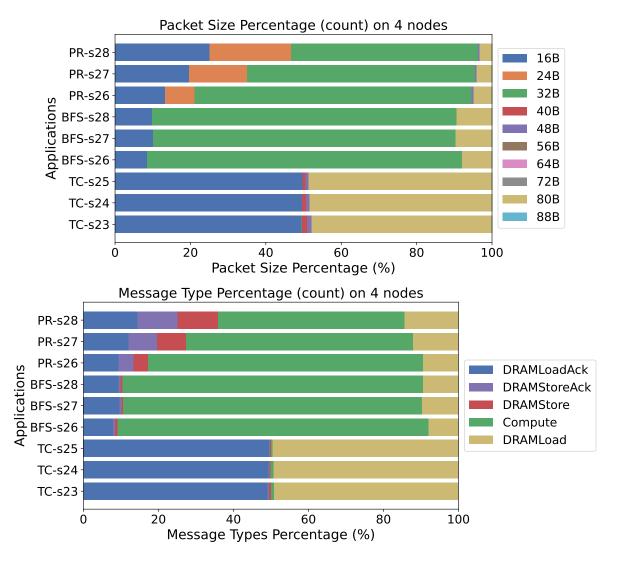

| 4.16       | Distribution of network packet sizes (upper) and packet type ratios (lower) at 32                                                                                                                                                                                                                                                                                                                                                                                                                   | 46             |

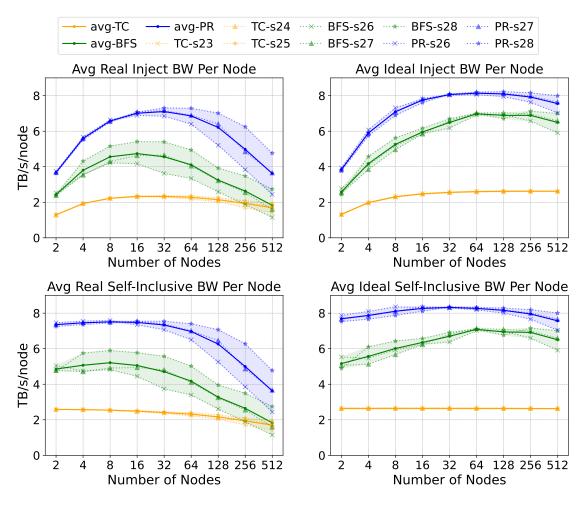

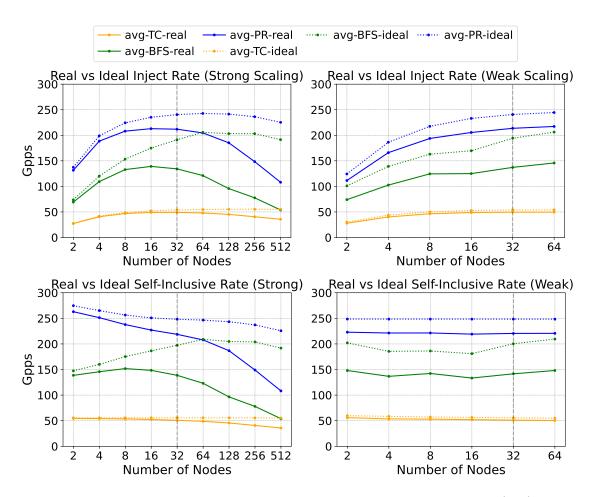

| 4.17       | Real (left) and Ideal (right) Average Network Injection Bandwidth Per Node                                                                                                                                                                                                                                                                                                                                                                                                                          | 47             |

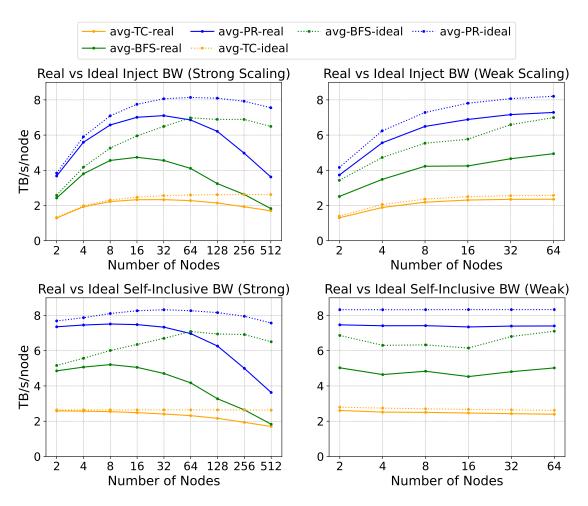

| 4.18       | Network Injection Bandwidth Per Node on Strong Scaling (left) and Weak Scaling                                                                                                                                                                                                                                                                                                                                                                                                                      | 49             |

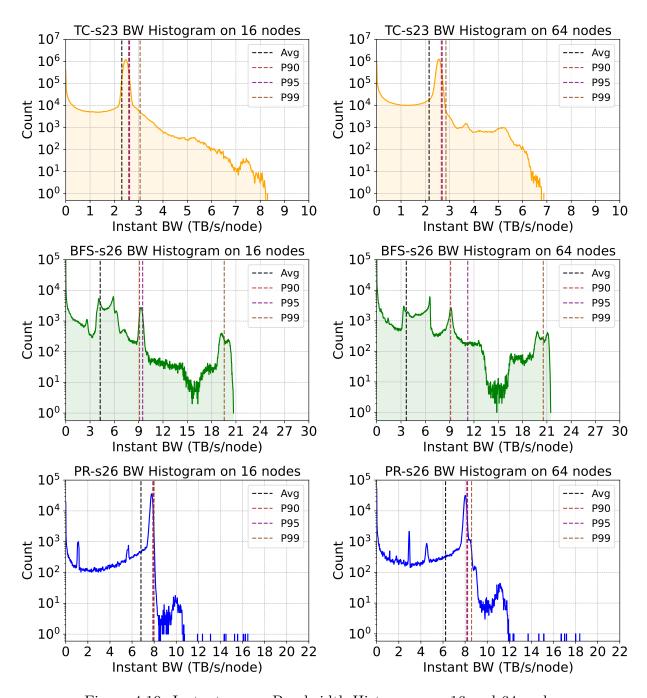

| 4.19       | Instantaneous Bandwidth Histogram on 16 and 64 nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51             |

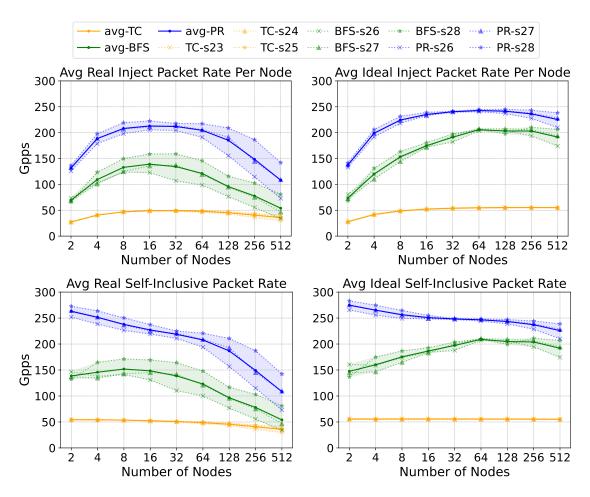

|            | Real (left) and Ideal (right) Average Network Packet Injection Rate Per Node                                                                                                                                                                                                                                                                                                                                                                                                                        | 52             |

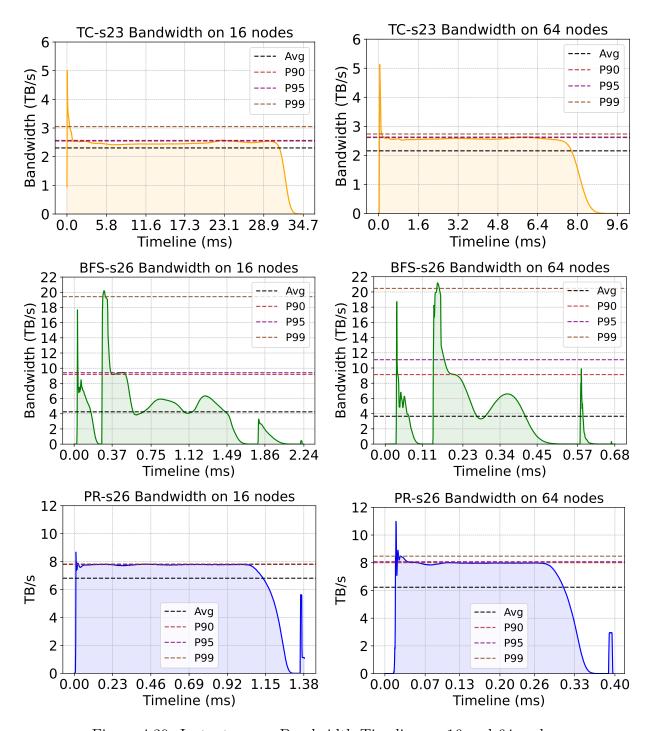

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54             |

| 4.22       | Network Packet Injection Rate Per Node on Strong Scaling (left) and Weak Scal-                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 4.00       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55             |

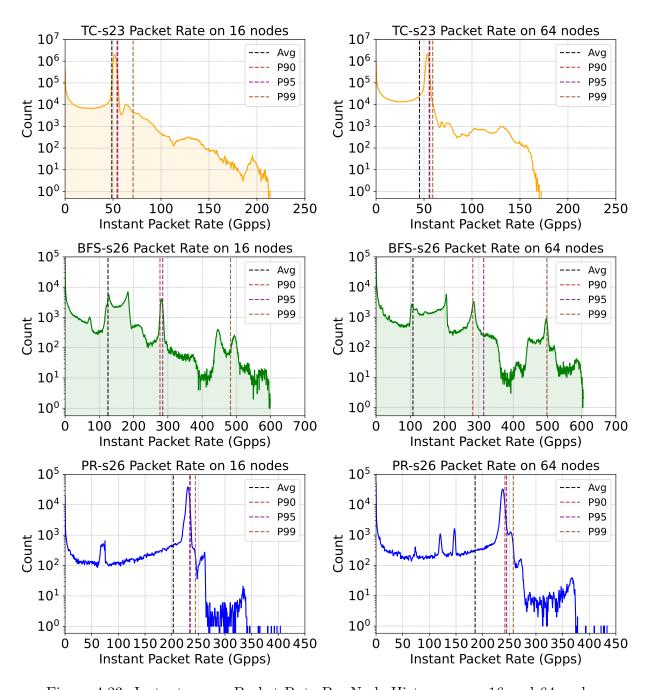

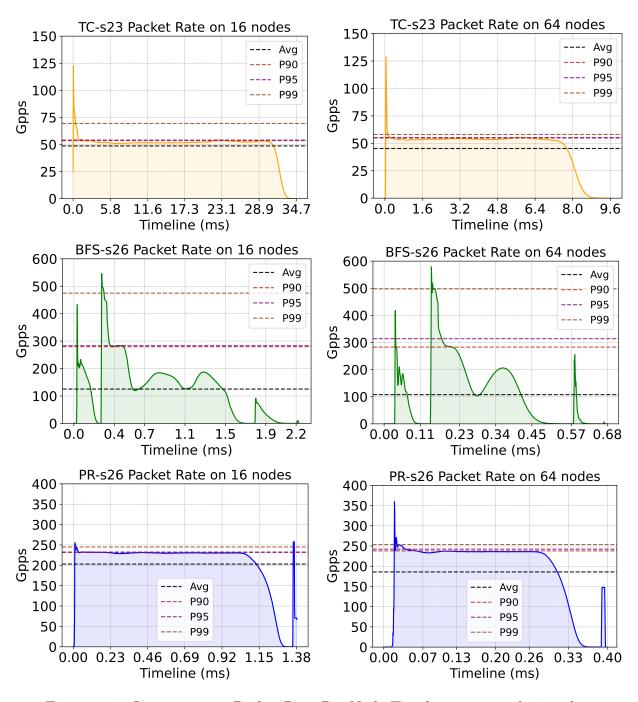

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57             |

| 4.24       | Instantaneous Packet Rate Per Node Timeline on 16 and 64 nodes                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58             |

| 5.1        | Network Latency Influence on UpDown. (Remote DRAM latency = 6)                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62             |

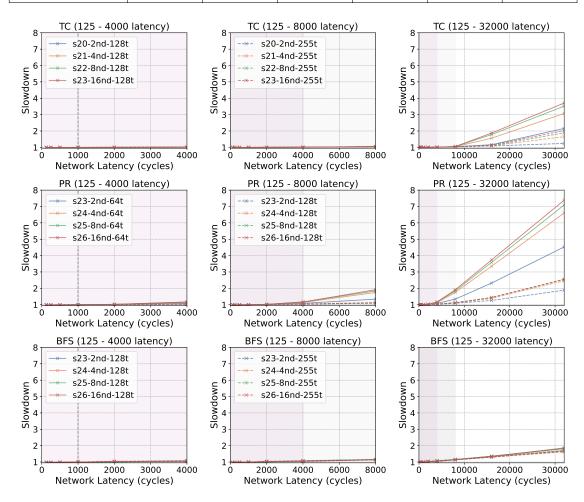

| 5.2        | Slowdown across different network latency (baseline 1000-cycle network latency), first row is TC, second row is PR, third row is BFS under network latency between                                                                                                                                                                                                                                                                                                                                  |                |

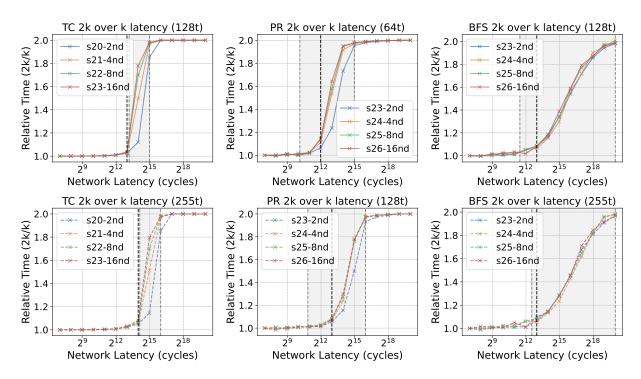

| 5.3        | Relative Execution Time on 2k latency over k latency. First column is TC, second column is PR, third column is BFS. The beginning of the gray region corresponds to the effective multi-thread parallelism, while the end marks the highest latency value at which some latency hiding is still effective (i.e., speedup approaches 2). The shaded gray region represents the range of internal-parallelism latency tolerance. The dotted black line indicates the maximum tolerant network latency | 6 <sup>2</sup> |

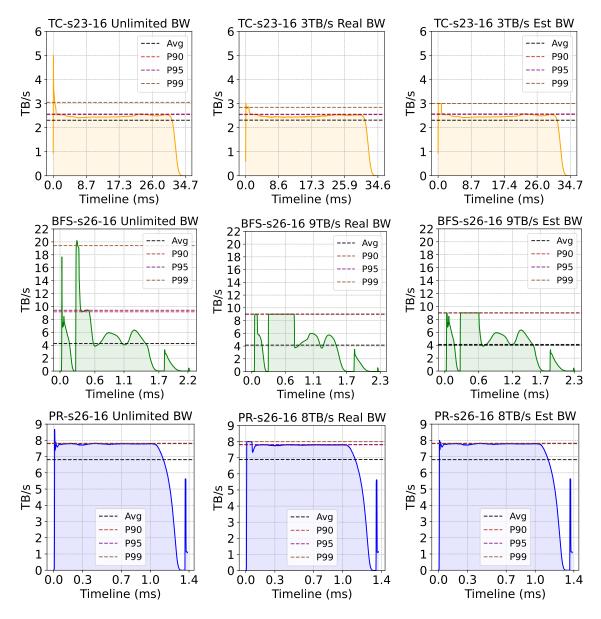

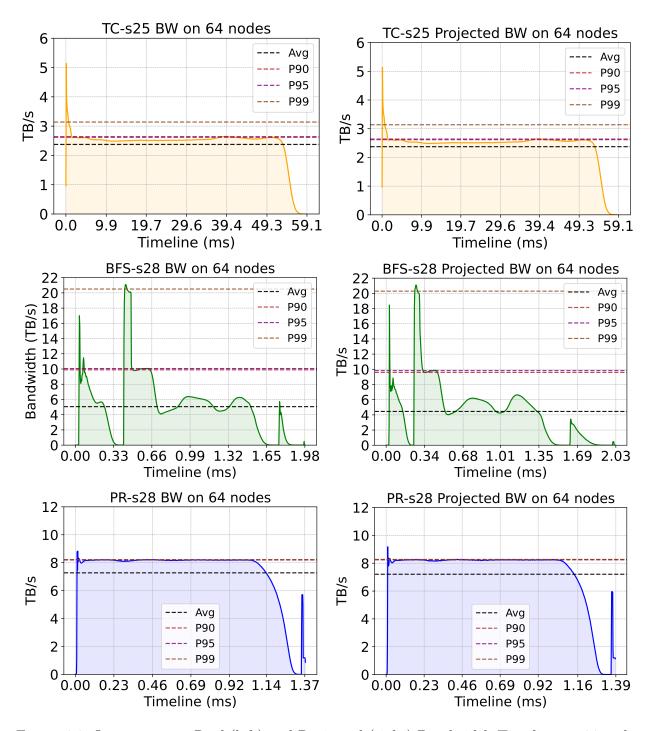

| 5.4<br>5.5 | Relative Performance versus network injection bandwidth limitation Instantaneous bandwidth over time for each application: unlimited injection                                                                                                                                                                                                                                                                                                                                                      | 67             |

|            | bandwidth (first column), P95 or P99 injection bandwidth limitation (second                                                                                                                                                                                                                                                                                                                                                                                                                         | 68             |

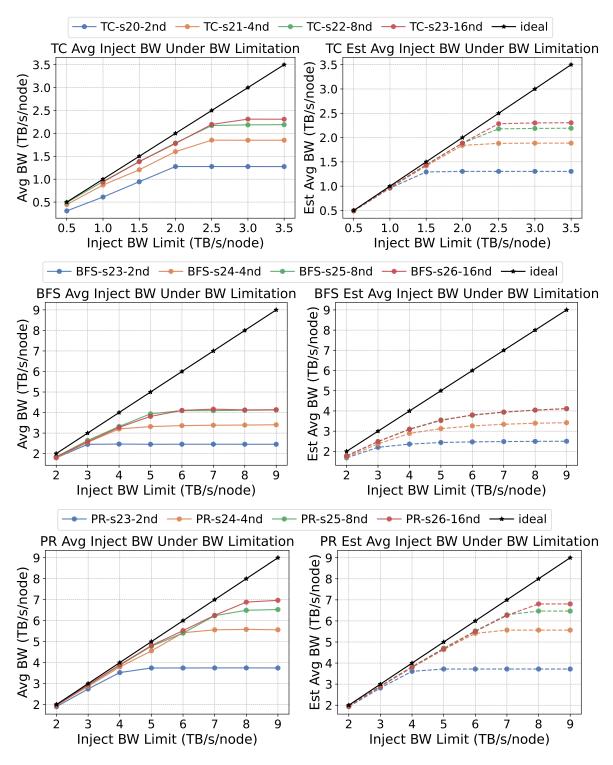

| 5.6        | The average network injection bandwidth per node under different injection band-                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.             |

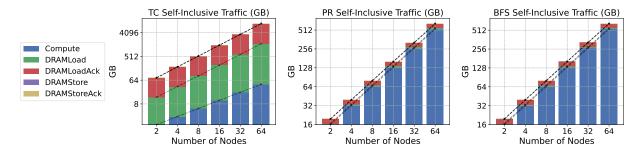

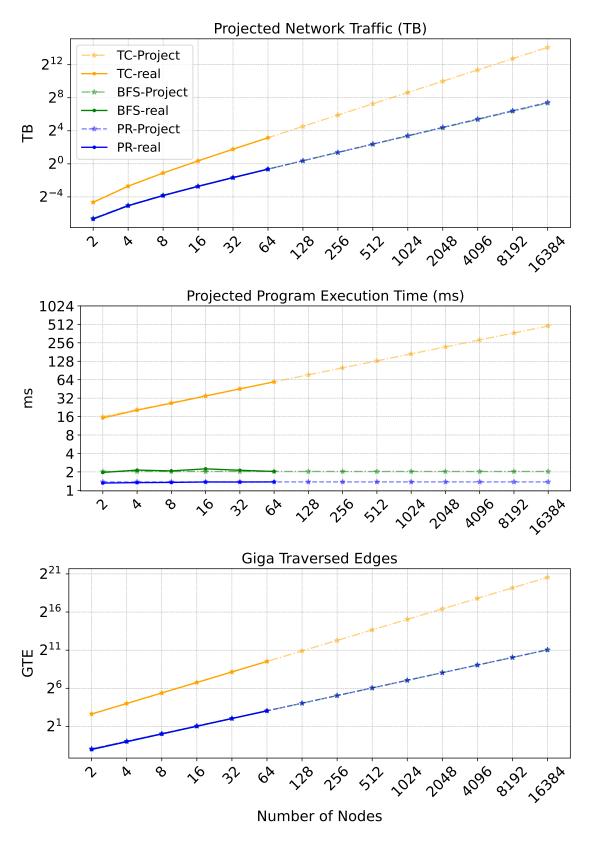

| 6.1        | Total Network Traffic (GB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75             |

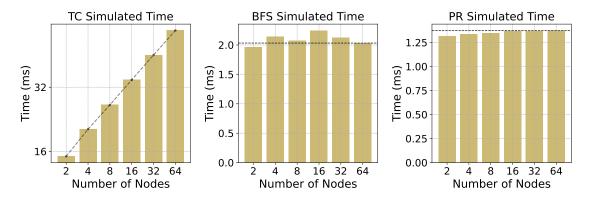

| 6.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70             |

| 6.3        | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77             |

| 6.4        | Projected and Real Network Traffic, Execution Time, and Traversed Edges on                                                                                                                                                                                                                                                                                                                                                                                                                          | 79             |

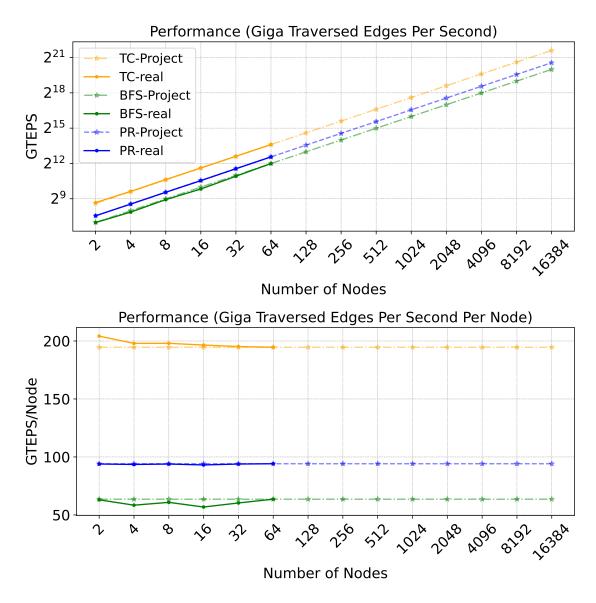

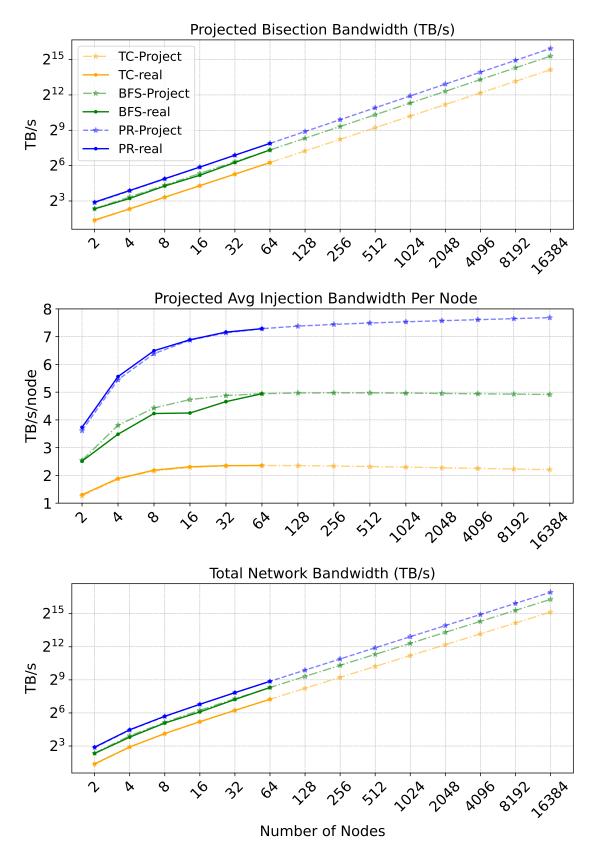

| 6.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8(             |

| 6.6        | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8              |

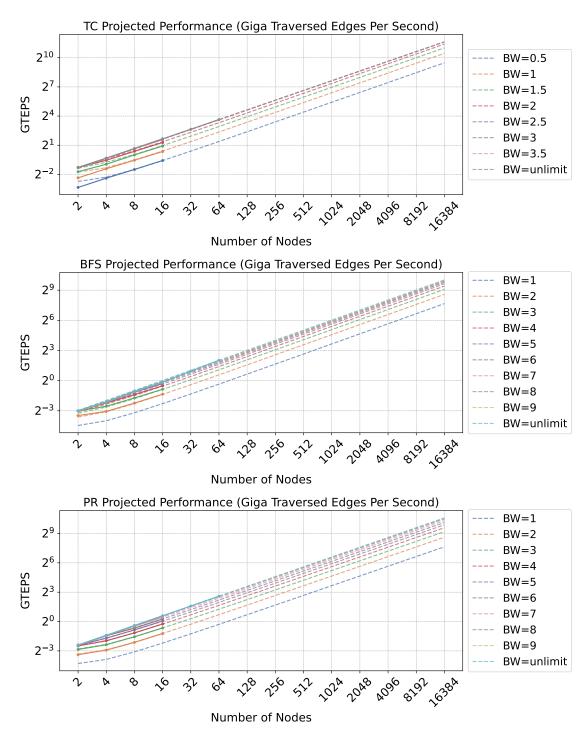

| 6.7 | Projected and Real Performance (GTEPS) under different network injection band- |    |

|-----|--------------------------------------------------------------------------------|----|

|     | width per node constrain on 2-16384 nodes                                      | 83 |

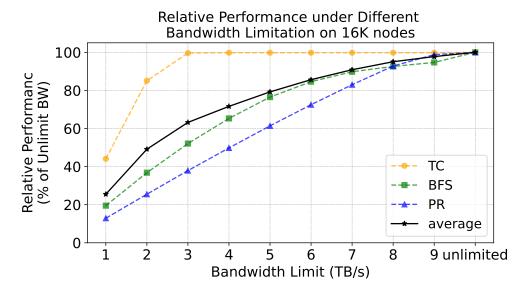

| 6.8 | Relative Performance under Different Bandwidth Limitation on 16K nodes (base-  |    |

|     | line is unlimited network injection bandwidth limitation)                      | 84 |

# LIST OF TABLES

| 2.1 | Different I/O Channel Bandwidth                                                                                                                          | 5  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Ethernet II Packet Format [4]                                                                                                                            | 7  |

| 2.3 | NVLink Packet [5]                                                                                                                                        | 9  |

| 2.4 | Top500 HPC Systems [6]                                                                                                                                   | 16 |

| 2.5 | NVIDIA HPC Systems and UpDown                                                                                                                            | 17 |

| 3.1 | UpDown Instruction Set Architecture Highlights                                                                                                           | 20 |

| 3.2 | Event Word and Address Encoding                                                                                                                          | 21 |

| 3.3 | UpDown Packet Description                                                                                                                                | 24 |

| 3.4 | Benchmark Applications                                                                                                                                   | 25 |

| 3.5 | UpDown System Configuration                                                                                                                              | 26 |

| 4.1 | Metrics and Description                                                                                                                                  | 27 |

| 4.2 | Input Graph Dataset                                                                                                                                      | 28 |

| 4.3 | Weak Scaling Input Graphs                                                                                                                                | 33 |

| 4.4 | Breakdown of Program Characteristics on 32 nodes. (KI: Kilo Instructions)                                                                                | 36 |

| 4.5 | Average Network Injection Bandwidth Per Node                                                                                                             | 49 |

| 4.6 | Average Network Packet Injection Rate Per Node                                                                                                           | 56 |

| 4.7 | Average Network Packet Injection Rate Per Core (2GHz)                                                                                                    | 56 |

| 5.1 | Latency Tolerance Features Usage on TC, PR and BFS                                                                                                       | 63 |

| 5.2 | Multi-thread Parallelism on TC, PR and BFS                                                                                                               | 63 |

| 5.3 | Maximum Network Latency Cycles Applications $<20\%$ Performance Degradation.                                                                             | 64 |

| 6.1 | Projected input graph                                                                                                                                    | 73 |

| 6.2 | Projected Data on Full-scale UpDown System                                                                                                               | 82 |

| 6.3 | Full-scale UpDown system performance (GTEPS) under different network injection bandwidth per node constrain (project method is shown in Section 6.1.3) . | 84 |

| 7.1 | Estimated application performance under varying network injection requirements                                                                           | 85 |

# ABSTRACT

The UpDown System is a novel fine-grained, event-driven architecture designed for irregular graph computation, that has demonstrated scalable performance to 16,384 nodes. Due to its unique event-driven mechanism, UpDown exhibits distinct computation and DRAM access patterns compared to conventional architectures such as CPUs and GPUs, thus, UpDown has different network communication characteristics. Understanding the network traffic patterns generated by UpDown applications—and how parameters such as latency and injection bandwidth impact performance—is critical for system designers to identify appropriate network configurations.

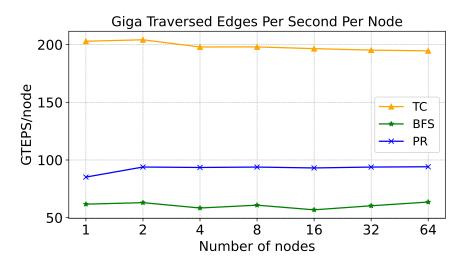

In this thesis, we simulate three irregular graph applications—Triangle Counting (TC), Breadth-First Search (BFS), and PageRank (PR)—on 1 to 512 UpDown nodes under varying network latencies and injection bandwidth constraints, and we project performance trends for a 16,384-node system. Results show that UpDown applications generates uniform traffic across nodes, with packet sizes ranging from 16 to 88 bytes. These applications produce approximately 0.5 to 2 bytes of network traffic per instruction, requiring 2–8 TB/s of injection bandwidth per node. Moreover, system performance remains stable under constrained injection bandwidth and increased network latencies of up to 4000 ns (8 times that of the hardware designed), indicating strong resilience to both transient bandwidth fluctuations and network designs that deliver longer communication delays.

#### CHAPTER 1

#### INTRODUCTION

Over the past several decades, the emergence of "internet-scale" and other big data workloads has driven a growing demand for computing systems capable of efficiently processing large-scale data, such as graphs with hundreds of billions of edges [7, 8]. To meet this growing demand, modern computing systems must scale both per-node performance and the total number of nodes. Consequently, many large-scale system [9, 10, 11, 12, 13, 14, 15, 16, 17] and cloud platforms have been built with thousands of nodes to deliver performance in the range of hundreds to thousands of PFLOPS.

Large-scale system architectures can broadly be classified into two categories: 1) Distributed memory architectures, which use MPI communication protocols between nodes —examples include Fugaku and Tianhe [9, 18]; 2) Shared memory architectures, which integrate RDMA technologies to enable high-performance memory access across nodes, such as the NVIDIA DGX GH200 system [19, 20, 21, 22, 23]. As shown in Figure 1.1, distributed memory architectures using MPI can demonstrate reasonable scalability at modest system sizes. However, as the number of nodes or cores increases, scalability bottlenecks emerge—primarily due to communication overhead. In distributed memory systems, MPI introduces substantial communication overhead, including eager polling for progress, inefficient global synchronization, and thread contention. These factors contribute to sub-linear performance scaling at scale [1, 9]. For applications with regular computation patterns, such as dense matrix multiplication—which exhibits coarse-grained parallelism and large per-thread workloads—MPI systems can scale efficiently by overlapping communication and computation through multi-threading. However, for irregular applications like Breadth-First Search (BFS) and PageRank (PR), the communication is fine-grained and data-dependent, leading to high synchronization costs and communication overhead. As a result, network traffic and thread contention dominate execution time, limiting scalability and overall per-

Figure 1.1: The solid line is the real performance, and the dashed line is the linear performance. (a) and (b): Weak scaling performance results using RMAT graphs of scale 25 to 35 on the Blue Gene/Q system. The MPI-CPU configuration utilizes 16 processes per node, while the hybrid configuration (MPI+OpenMP) employs 1 process per node and 16 threads per node [Adapted from [1]]. (c) Weak scaling performance with scale 26 RMAT graphs on each Tesla P100 GPU up to 124 GPUs on an early access system (Ray) of LLNL's upcoming CORAL/Sierra supercomputer [Adapted from [2]]. (d) Weak scaling performance using RMAT graphs of scale 22 to 28 on the UpDown system.

formance [1]. Additionally, porting applications from single-node to distributed environments often requires substantial code modification to integrate MPI interfaces. While regular workloads such as transformer-based language models can achieve near-linear scaling across GPUs in shared memory systems with RDMA [24], training still demands significant inter-node communication, which can become a bottleneck when network bandwidth is limited [25].

Irregular graph algorithms—such as Breadth-First Search (BFS) and PageRank—further exacerbate scalability challenges due to their high inter-node traffic and page invalidation overheads [26], resulting in degraded scalability and sub-linear performance gains [27, 28].

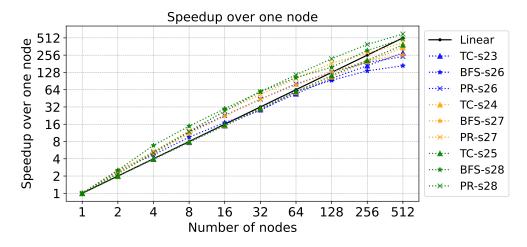

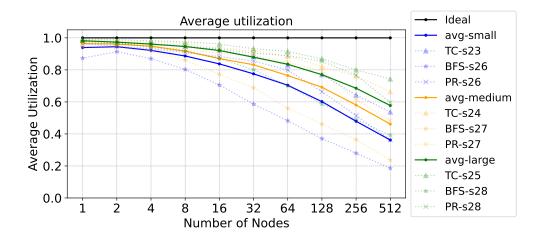

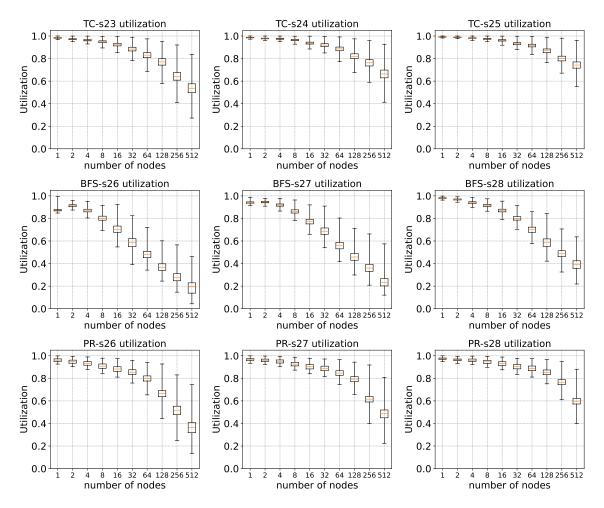

In contrast, UpDown—a fine-grained, event-driven, globally addressable distributed memory architecture—can achieve linear scalable performance across multiple nodes (Figure 1.1(d)) without requiring any code modifications from the single-node implementation. To demonstrate this, we simulate three irregular graph applications—Triangle Counting (TC), Breadth-First Search (BFS), and PageRank (PR)—across 1 to 512 nodes, analyzing their scalability and network communication patterns. Furthermore, we conduct sensitivity studies on network latency and injection bandwidth, revealing that these applications exhibit strong resilience to both transient bandwidth fluctuations and prolonged communication delays on the UpDown system. Finally, we project performance results for a full 16,384-node UpDown system and compare its scalability and efficiency with existing large-scale systems.

The main contributions of this thesis are as follows:

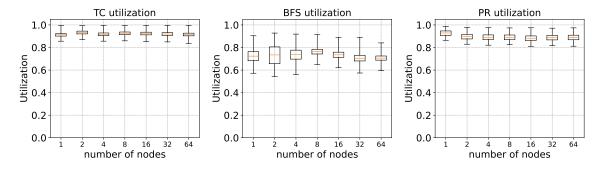

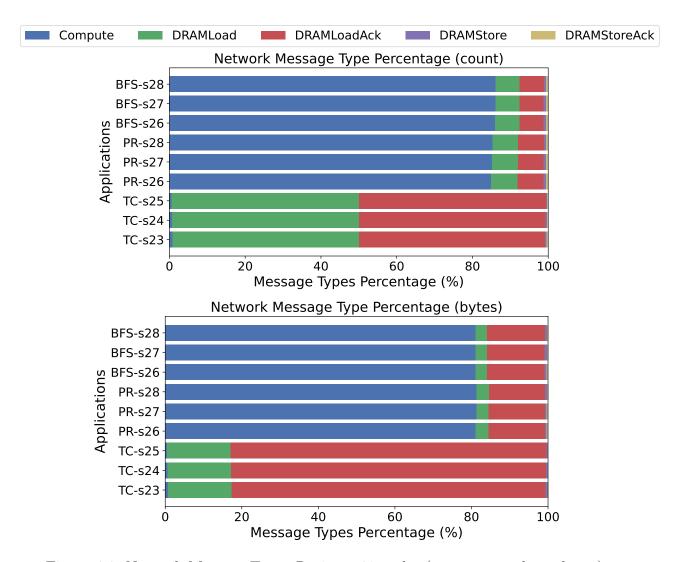

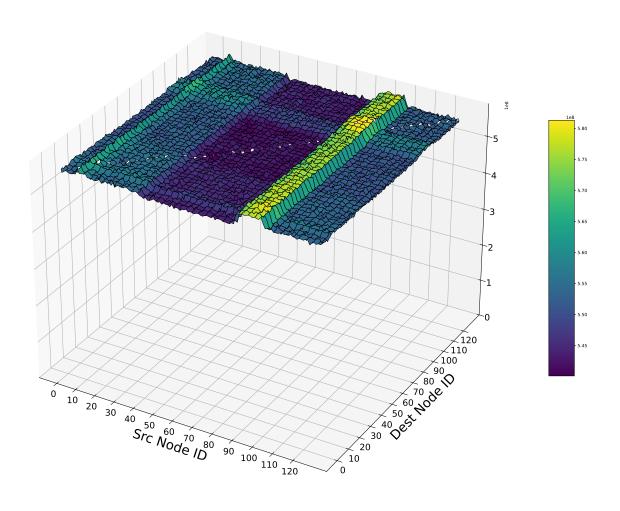

- 1. We demonstrate that UpDown graph applications achieve scalable performance across multi-node systems with high resource utilization and no code modifications.

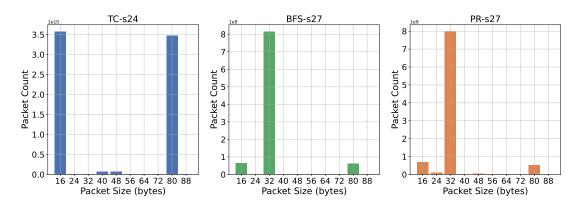

- 2. We analyze the network traffic patterns generated by UpDown applications, and show they exhibit uniform traffic across nodes with packet sizes ranging from 18 to 88 bytes—most commonly 16 B, 32 B, and 80 B—and generate 2–8 TB/s of network injection bandwidth per node.

- 3. We evaluate system robustness and show that UpDown maintains high performance under both transient bandwidth fluctuations and long communication latencies, demonstrating strong resilience across diverse network conditions.

- 4. We project the performance of a full-scale 16,384-node UpDown system, where Triangle Counting (TC), Breadth-First Search (BFS), and PageRank (PR) achieve 3,181,388

GTEPS, 1,041,354 GTEPS, and 1,542,398 GTEPS, respectively. We also estimate performance under different network injection bandwidth constraints.

We begin by introducing the background in Chapter 2, covering key concepts such as IO bandwidth, packet formats, frame forwarding rates, and large-scale system configurations. The design of the UpDown architecture and its network packet format is presented in Chapter 3. Scaling performance and communication characteristics across 1–512 nodes are evaluated in Chapter 4, followed by a sensitivity analysis of network latency and injection bandwidth in Chapter 5. We then project weak-scaling performance for configurations up to 16,384 nodes under different network assumptions in Chapter 6, and summarize key network requirements and future work in Chapter 7.

## CHAPTER 2

#### BACKGROUND

This chapter provides an overview of the current landscape of network bandwidth capabilities, packet formats, and frame forwarding rates supported by network devices in large-scale computing systems.

# 2.1 I/O Channel Bandwidth and Emerging Technologies

Input/Output (I/O) Channel Bandwidth refers to the data transmission rate of communication channels, typically measured in gigabits per second (Gbps). It represents the rate at which data is transmitted through chip-to-chip interconnects, such as Ethernet, InfiniBand, Slingshot, and NVLink. The current progress in I/O channel bandwidth primarily depends on advancements in serial/parallel signal transmission technology, modulation methods, and packaging techniques.

Table 2.1: Different I/O Channel Bandwidth

| Name       | Year | Channel Bandwidth | Channel latency | Packet Size | Systems                      |

|------------|------|-------------------|-----------------|-------------|------------------------------|

| Ethernet   | 2014 | 100-400 Gbps      | 2-10 us         | 64B-9KB     | NVIDIA DGX A100/ROCEv2       |

| InfiniBand | 2018 | 200-400 Gbps      | 0.5-1 us        | 64B-9KB     | Summit, Fugaku               |

| Slingshot  | 2019 | 100-200 Gbps      | 1 us            | 32B-9KB     | El Capitan, Frontier, Aurora |

| NVLink     | 2017 | 200-400 Gbps      | 0.5 us          | 16-288B     | DGX GH200, GB200 NVL72       |

As bandwidth demands increase, I/O systems face growing challenges, including signal attenuation, elevated power consumption, and physical limitations at the package level. When transmission rates exceed thresholds such as 112 Gbps using PAM4 signaling, signal integrity deteriorates sharply, restricting PCB trace lengths to only a few centimeters. Simultaneously, each additional SerDes channel in high-speed transmission contributes significantly to power consumption. As channel bandwidth increasing, I/O channel power becomes a critical bottleneck for system-level energy efficiency. Moreover, the limited area of chip packages imposes constraints on the number of I/O channels due to wiring density

and thermal design limitations [29]. Consequently, despite differences in network architecture and protocols, the per-channel bandwidth across Ethernet, InfiniBand, and Slingshot is not substantially different, as all are subject to similar physical and power constraints.

# 2.1.1 Co-Packaged Optics (CPO)

Co-Packaged Optics (CPO) addresses key limitations in traditional electrical interconnects, such as bandwidth bottlenecks, and excessive power consumption. By integrating optical modules directly into computing chips or switching chips, CPO effectively overcomes signal attenuation and crosstalk issues. It also eliminates the performance degradation and energy inefficiencies associated with long copper links, thereby significantly increasing bandwidth density.

Ayar Labs has introduced the TeraPHY optical chiplet, capable of achieving 8 Tbps using a 16-wavelength SuperNova light source [30]. Broadcom has announced plans to integrate CPO into its compute ASICs, targeting 12.8 Tbps (6.4 Tbps per direction) by 2025, with an ambitious roadmap to scale up to 102.4 Tbps (51.2 Tbps per direction) by 2028 [31]. This breakthrough technology is expected to meet the growing demands of AI, HPC, and large-scale data centers. By leveraging CPO, these systems can achieve high-bandwidth, low-power, and low-latency interconnects—surpassing the physical and energy efficiency limitations of conventional electrical signaling.

#### 2.2 Network Packet Format

Networks implement different protocols and packet formats across various OSI layers: Ethernet operates at the data link layer, IPv4/IPv6 at the network layer, and UDP/TCP at the transport layer. To reduce protocol overhead and improve data transmission efficiency, modern high-performance interconnects—such as HPE Slingshot and NVIDIA NVLink—typically employ lightweight, customized packet formats that bypass or simplify the traditional net-

work and transport layers.

# 2.2.1 Ethernet Packet Format

Table 2.2: Ethernet II Packet Format [4]

| Layer            | Field                       | Size      | Description                             |

|------------------|-----------------------------|-----------|-----------------------------------------|

|                  | Inter frame gap             | Min 12B   | An inter frame gap is required be-      |

|                  |                             |           | tween Ethernet frames, meaning          |

|                  |                             |           | that a device must wait for a speci-    |

|                  |                             |           | fied period before sending each sub-    |

| Dharaical larran |                             |           | sequent frame. This is necessary to     |

| Physical layer   |                             |           | give the frame receiver enough time     |

|                  |                             |           | to process each frame. The length       |

|                  |                             |           | can be reduced to 64 bits for GE in-    |

|                  |                             |           | terfaces or 40 bits for 10GE inter-     |

|                  |                             |           | faces.                                  |

|                  | Preamble                    | 7B        | Synchronizes the receiver before ac-    |

|                  |                             |           | tual data transmission                  |

|                  | Start Frame Delimiter (SFD) | 1B        | Indicates the start of the Ethernet     |

|                  |                             |           | frame                                   |

|                  | Dest MAC Address (DMAC)     | 6B        | Address of the receiving device         |

|                  | Source MAC Address (SMAC)   | 6B        | Address of the sending device           |

| Link layer       | EtherType                   | 2B        | Specifies the protocol encapsulated     |

| Lilik layer      |                             |           | in the payload (e.g., $IPv4 = 0x0800$ ) |

|                  | Payload (Data)              | 46B-1500B | Actual data being transmitted           |

|                  | Frame Check Sequence (FCS)  | 4B        | CRC checksum for error detection        |

The traditional Ethernet packet format adheres to a standardized frame structure that is widely adopted in LAN and Internet communication. An Ethernet II frame consists of a 13–20 byte physical layer header and an 18-byte data link layer header, resulting in a total header size of 31–38 bytes. The data payload typically ranges from 46 to 1500 bytes, yielding a payload efficiency of approximately 54% (with a 46-byte payload) to 98% (with a 1500-byte payload), depending on the payload size.

To enhance transmission efficiency for large data transfers, Ethernet networks support jumbo frames—packets with a larger Maximum Transmission Unit (MTU) than the standard Ethernet frame. These frames are widely supported and commonly enabled in high-

performance NICs and switches, particularly in HPC environments. By reducing the number of packets required to transmit a given volume of data, jumbo frames help lower CPU utilization and protocol processing overhead. An MTU size of 9 KB is generally recommended for Ethernet-based HPC networks, as it enables more efficient frame handling, improved throughput, and reduced packet overhead [32]. In systems using HPE Cray interconnects, when InfiniBand is configured as the high-speed network, the default MTU is typically set to 64 KB. This configuration supports jumbo frame traffic and is considered optimal for IP over InfiniBand (IPoIB), maximizing bandwidth utilization for large-message communication [33].

# 2.2.2 HPE Slingshot Packet Format

Ethernet was originally designed for local and wide area networks, rather than the tightly coupled communication required in supercomputing environments. Its relatively large packet overhead, lower switching rates compared to HPC standards, and reliance on packet drops under congestion make Ethernet poorly suited for latency-sensitive protocols such as remote direct memory access (RDMA), widely used in HPC and storage systems.

HPE Slingshot [34, 35] enhances standard Ethernet by extending the Link Layer Discovery Protocol (LLDP) and introducing a packet format optimized for HPC fabrics. Slingshot supports standard Ethernet at the edge while employing optimized HPC-specific Ethernet on internal network links.

Compared to Ethernet, Slingshot packets support smaller minimum frame sizes of 32 or 40 bytes [35, 36], making them well-suited for single-word (8 B) remote memory access operations. While Slingshot's public documentation does not specify a maximum MTU, it has demonstrated effective performance with message sizes up to 128 KB [35]. To support Slingshot's flexible packet structure and associated protocols, the packet header typically ranges from 24 to 32 bytes—larger than the 13–20 byte header used in standard Ethernet II frames. As a result, the payload-to-header ratio varies significantly depending on the

message size, with payload efficiency ranging from approximately 20% for small payloads (e.g., 8 bytes of data) to nearly 99.975% for large payloads (e.g., 128 KB).

## 2.2.3 NVLink Packet Format

NVLink [5] provides fine-grained, high-bandwidth, and low-latency communication between processors and memory. A typical NVLink transaction consists of a request and its corresponding response. NVLink packets vary in size, ranging from a single 128-bit flit (16 bytes) to as many as 18 flits (288 bytes), enabling data transfers of up to 256 bytes.

Table 2.3: NVLink Packet [5]

| Field                            | Size     | Description                                      |

|----------------------------------|----------|--------------------------------------------------|

| Cyclic redundancy check (CRC)    | 25 bits  | Detect data errors                               |

| Transaction layer header         | 83 bits  | Request type, address, flow control credits,     |

|                                  |          | and tag identifier                               |

| Data link layer heder            | 20 bits  | Acknowledge identifier, packet length infor-     |

|                                  |          | mation, and application number tag               |

| Address extension (AE, optional) | 128 bits | AE flit contains information that should         |

|                                  |          | be relatively static from request to request     |

|                                  |          | (sticky bits), information that is command-      |

|                                  |          | specific, or information that alters the default |

|                                  |          | value for a command type. Sticky informa-        |

|                                  |          | tion is transmitted when it changes and is       |

|                                  |          | stored on the receiver side for reuse for non-   |

|                                  |          | AE packets.                                      |

| Byte enable (BE, optional)       | 128 bits | A BE flit is used for write or atomic com-       |

|                                  |          | mands, and 128 enable bits indicate the data     |

|                                  |          | bytes to be written on writes up to 128 bytes.   |

| Data payload                     | 0-256B   | Between 0 and 16 128-bit data payload flits      |

NVLink packets transmit data in units of 16 bytes (128-bit flits). Excluding AE (Address Extension) and BE (Byte Enable), the packet header occupies only 16 bytes, with data payloads ranging from 0 bytes up to 256 bytes. Consequently, the payload can constitute up to approximately 94% of the packet (16-byte header plus 256-byte data payload). NVLink employs a highly compact packet header format relative to other contemporary network protocols.

# 2.3 Packet Frame Forwarding Rate

The packet forwarding rate of a network NIC or switch is a key indicator of its processing capacity. It represents the number of packets the device can handle per second, typically measured in millions of packets per second (Mpps) or millions of messages per second (Mmps).

# 2.3.1 HPE Slingshot CASSINI NIC and Rosetta Switch

Cassini [35] is a 200 Gbps HPC NIC ASIC developed by HPE. The host interface is PCIe Gen4 and supports extended speed mode. The network link port conforms to the Ethernet standards for 200 Gbps ( $4\times50$  Gbps PAM4) or 100 Gbps ( $4\times25$  Gbps NRZ).

Figure 2.1 illustrates remote memory access (RMA) bandwidth as a function of data size in message for 64 processes per NIC, measured using a SHMEM performance test on a single Cassini NIC in the Shadow system. For 8-byte data payloads, a Cassini NIC achieves a packet forwarding rate of 189 million packets per second (Mpps), corresponding to an effective port data bandwidth of 12.1 Gbps (60.5 Gbps including a 32-byte packet header). For 64-byte frames, the built-in frame generator records a forwarding rate of 155 Mpps, yielding a port data bandwidth of 79.4 Gbps (119 Gbps with 32-byte headers). For 1024-byte data payloads, the forwarding rate is 22.8 Mpps, corresponding to 186 Gbps effective bandwidth (192 Gbps with headers included).

# 2.3.2 NVLink4 and NVLink4 Switch

NVSwitch4 is an NVLink switch chip that integrates 18 NVLink4 ports, internally organized as an 18×18 fully connected crossbar [37]. This architecture enables any port to communicate with any other at the full NVLink speed of 50 GB/s, yielding an aggregate switch bandwidth of 900 GB/s. Each NVLink4 port provides 25 GB/s per direction. Each GPU can be connected via up to 18 NVLink4 interfaces to switches or directly to other GPUs, offering a

Figure 2.1: Remote memory access bandwidth and message rate as a function of data payload size in message for 64 processes per NIC on the Shadow system. [Adapted from [3]].

total bidirectional bandwidth of 900 GB/s (450 GB/s per direction).

As publicly available data on NVSwitch frame forwarding rates is limited, the theoretical forwarding rate is estimated based on NVLink's port bandwidth and packet sizes. For the smallest packet size of 16 bytes, each port can achieve a maximum forwarding rate of approximately 3,125 million packets per second (Mpps). For 64-byte packets, the estimated forwarding rate is approximately 781 Mpps per port. For 256-byte packets, the estimated forwarding rate is approximately 195 Mpps per port.

# 2.3.3 51.2T TH5-Bailly

Broadcom's TH5-Bailly [31] is a state-of-the-art 51.2 Tbps Ethernet switch that leverages Co-Packaged Optics (CPO) technology to address the growing demands for high-bandwidth, low-power network interconnects in domains such as artificial intelligence (AI) and high-performance computing (HPC). The switch supports 128 × 400 Gbps FR4 optical connections. Assuming a packet size of 64 bytes, the theoretical packet forwarding rate per port is approximately 781 million packets per second (Mpps), resulting in an aggregate packet forwarding rate of 100 billion packets per second (Bpps) for the entire switch.

Figure 2.2: Message rate vs. message size for various high-speed interconnect technologies as of 2019. [Adapted from [3]]. **HPC Ethernet** refers to enhanced Ethernet (e.g., Slingshot) optimized for HPC with adaptive routing and low-latency transport. **HDR InfiniBand** delivers 200 Gbps using PAM4 signaling and low-latency RDMA, suitable for modern HPC and AI workloads. **EDR InfiniBand** provides 100 Gbps using NRZ, widely adopted in earlier HPC systems. **Aries** is Cray's proprietary interconnect, utilizing a Dragonfly topology with adaptive routing for low-latency communication. **RoCEv1** enables RDMA over Layer 2 Ethernet, requiring a lossless fabric and typically constrained to a single subnet.

# 2.3.4 Other HPC Interconnect technologies

We also evaluate message rate and packet-level bandwidth across other HPC interconnect technologies. As shown in Figure 2.2, their message forwarding rates range from 25 to 300 million packets per second (Mpps). Beyond link-level bandwidth constraints, message rate efficiency is also influenced by message size. As illustrated in Figure 2.2 and Figure 2.1(b), smaller message sizes do not lead to proportionally higher message rates and instead result in substantially lower packet bandwidth. This demonstrates that bandwidth utilization efficiency—defined as packet bandwidth (i.e., the product of message rate and message size)—declines for small messages due to protocol overhead, serialization delays, per-packet processing costs, and so on.

# 2.4 Large-scale systems

In this section, we summarize the network configurations and interconnect technologies used in various large-scale high-performance computing systems.

El Capitan [10, 11], Frontier [12], and Aurora [13] are the top three supercomputing systems in the world as of 2024. Fugaku [14, 15] remains the highest-performing non-GPU-based system and achieves the best Breadth-First Search (BFS) performance according to the TOP500 list [6]. Table 2.4 summarizes key architectural parameters of these systems, including core count, peak FP64 performance, memory bandwidth, and network injection bandwidth—both per node and at system scale. In addition, NVIDIA offers several GPU-based rack-scale systems with significantly higher inter-node bandwidth, as listed in Table 2.5. The top three supercomputing systems—El Capitan [10, 11], Frontier [12], and Aurora [13]—all employ HPE Slingshot interconnect technology. Fugaku utilizes Fujitsu's custom Tofu-D interconnect, while NVIDIA's GPU-based rack-scale systems use NVLink for intra-rack communication.

# 2.4.1 One Node Configuration

The following section compares the ratios between compute resources—measured as peak FP64 performance (excluding tensor cores)—memory bandwidth, and network injection bandwidth on a single compute node across several large-scale systems. Two key metrics are used for comparison: (1) the ratio of network to memory bandwidth, and (2) the amount of network traffic generated per 1,000 FP64 operations.

As shown in Table 2.4, El Capitan, Frontier, and Aurora deliver between 177 and 250 TFLOPS of peak FP64 performance, with memory bandwidths ranging from 13 to 21 TB/s per node. Despite their substantial computational and memory capabilities, these GPU-based systems provide only 100–200 GB/s of network injection bandwidth per node—representing just 0.5% to 1% of local memory bandwidth. As a result, the bandwidth

available for remote memory access is significantly lower than that of on-node memory, potentially constraining scalability for data-intensive applications. In addition, the average network traffic per 1,000 FP64 operations is 0.4 B, 0.5 B, and 1.13 B for El Capitan, Frontier, and Aurora, respectively. These values reflect a relatively low volume of network communication per unit of computation, underscoring the risk of network bottlenecks in both compute-bound and memory-bound workloads.

Fugaku is a purely CPU-based system, delivering 36.9 TFLOPS of FP64 performance per node. Due to its lower per-node compute and memory bandwidth, combined with a comparatively higher network injection bandwidth, Fugaku exhibits a higher ratio of network-to-memory bandwidth (4%) and a significantly higher network traffic rate—13 B per 1,000 FP64 operations. Nonetheless, the overall injection bandwidth remains relatively low compared to on-node resources.

NVIDIA's scale-up GPU-based platforms provide much higher network injection bandwidth per node: 450 GB/s with NVLink 4 and 1.8 TB/s with NVLink 5. The ratio of network-to-memory bandwidth improves from 5% (Grace Hopper) to 11% (Blackwell), and the network traffic per 1,000 FP64 operations is approximately 15–20 B—higher than current top500 supercomputer systems, but still lower than required for high-communication workloads

# 2.4.2 Whole Machine System Comparison

Most Top500 scalable machine systems adopt the Dragonfly network topology using 64-port HPE Slingshot network switches. Table 2.4 presents the system injection bandwidth, bisection bandwidth, BFS performance and energy for various systems. For Frontier, although the switch port design allows up to 50% bisection bandwidth, not all inter-group ports are utilized, resulting in an effective bisection bandwidth of only 30% of the system injection bandwidth. Aurora achieves a bisection bandwidth of 0.69 PB/s, which corresponds to 32.5% of its total system bandwidth. According to the Fugaku system slides [17], Fugaku reaches

only 94 TB/s of bisection bandwidth, accounting for merely 1.5% of the system bandwidth. But the network bandwidth inside one group is much higher. For NVIDIA systems, both DGX GH200 and GB200 NVL72 employ an all-to-all fat-tree topology, in which the bisection bandwidth is effectively half of the system's total network traffic capacity.

In addition, we incorporate Breadth-First Search (BFS) performance data from Graph500 [38]. Fugaku has consistently held the top BFS performance on RMAT scale 43 since 2020. Frontier currently ranks fourth, while Aurora ranks sixth. Despite delivering only one-quarter of the FP64 performance of Frontier and Aurora, Fugaku achieves 10× higher BFS performance, highlighting its architectural efficiency for graph-centric workloads.

Table 2.4: Top500 HPC Systems [6]

|                   | El Capitan [10, 11]   | Frontier [12, 39]                      | Aurora [13]                      | Fugaku [14, 15, 16, 17] |

|-------------------|-----------------------|----------------------------------------|----------------------------------|-------------------------|

| Compute Engines   | 4 AMD APU MI300A      | 1 AMD EPYC CPU                         | 2 Intel Xeon Max 9470 CPU        | 12 Fujitsu A64FX CPU    |

|                   |                       | 4 AMD MI250X GPU                       | 6 Intel Max 1550 GPU             |                         |

| Node CPU cores    | 96 @1.8GHz            | 64 @2GHz                               | 104 @2GHz                        | 576 @2GHz               |

| Node GPU CUs      | 912 @2.1 GHz          | 880 @1.7 GHz                           | 768 @900MHz                      |                         |

| Peak FP64 Perf    | 250.8 TFLOPS          | 212 TFLOPS                             | 176.9 TFLOPS                     | 36.9 TFLOPS             |

| Node Memory       | 512GB HBM3            | 512GB HBM2e(GPU)                       | 768GB HBM2e(GPU)                 | 384GB HBM2              |

|                   |                       | 512GB DDR4(CPU)                        | 128GB HBM2e(CPU)                 |                         |

|                   |                       |                                        | 1TB DDR5(CPU)                    |                         |

| Node Memory       | $21.2~\mathrm{TB/s}$  | $12.8~\mathrm{TB/s~HBM2e(GPU)}$        | $19.66~\mathrm{TB/s~HBM2e(GPU)}$ | $12~\mathrm{TB/s}$      |

| ${\bf Bandwidth}$ |                       | $205~\mathrm{GB/s}~\mathrm{DDR4(CPU)}$ | 2.87 TB/s HBM2e(CPU)             |                         |

|                   |                       |                                        | $0.56~\mathrm{TB/s~DDR5(CPU)}$   |                         |

| Network Type      | Slingshot             | Slingshot                              | Slingshot                        | Infiniband              |

| Node Ports        | 4                     | 4                                      | 8                                | 72                      |

| Node Injection    | $100~\mathrm{GB/s}$   | $100~\mathrm{GB/s}$                    | $200~\mathrm{GB/s}$              | $490~\mathrm{GB/s}$     |

| Bandwidth         |                       |                                        |                                  |                         |

| Network/Memory    | 0.46%                 | 0.76%                                  | 0.99%                            | 3.98%                   |

| Bandwidth         |                       |                                        |                                  |                         |

| Network Traffic   | 0.40 B                | 0.47 B                                 | 1.13 B                           | 13.28 B                 |

| Per 1k FP64       |                       |                                        |                                  |                         |

| Nodes             | 11,136                | 9,408                                  | 10,624                           | 13,248                  |

| CPU cores         | 1,069,056 @1.8GHz     | 602,112 @2GHz                          | 1,104,896 @2GHz                  | 7,630,848 @2GHz         |

| GPU CUs           | 10,156,032 @2.1GHz    | 8,279,040 @1.7GHz                      | 8,159,232 @900MHz                |                         |

| Peak FP64 Perf    | 2,793 PFLOPS          | 1,994 PFLOPS                           | 1,879 PFLOPS                     | 488 PFLOPS              |

| System Memory     | 5.4PB HBM3            | 4.6PB HBM2e(GPU)                       | 8.16PB HBM2e(GPU)                | 4.85PB HBM2             |

|                   |                       | 4.6PB DDR4(CPU)                        | 1.36PB HBM2e(CPU)                |                         |

|                   |                       |                                        | 10.9PB DDR5(CPU)                 |                         |

| System Ports      | 44,544                | 37,632                                 | 84,992                           | 953,856                 |

| System Injection  | $1.09~\mathrm{PB/s}$  | $0.90~\mathrm{PB/s}$                   | $2.12\mathrm{PB/s}$              | $6.19~\mathrm{PB/s}$    |

| Bandwidth         |                       |                                        |                                  |                         |

| Bisection         |                       | $0.27~\mathrm{PB/s}$                   | $0.69~\mathrm{PB/s}$             | $94~\mathrm{TB/s}$      |

| Bandwidth         |                       | (30%)                                  | (32.5%)                          | (1.5%)                  |

| Network Topology  | Dragonfly             | Dragonfly                              | Dragonfly                        | Tofu Interconnect D     |

|                   |                       |                                        |                                  | (6D mesh/torus)         |

| Network Switch    | HPE Slingshot         | HPE Slingshot                          | HPE Slingshot                    | Tofu Network Router     |

|                   | (64 ports @ 200 Gbps) | (64 ports @ 200 Gbps)                  | (64 ports @ 200 Gbps)            | (10 ports with 2 lanes) |

| Power             | 34.8 MW (Peak)        | 8-30 MW                                | 60 MW                            | 30-40 MW                |

| BFS GTEPS         |                       | 29,654.6                               | 24,250.2                         | 204,068                 |

Table 2.5: NVIDIA HPC Systems and UpDown

|                        | NVIDIA DGX GH200 [19, 20, 21, 22]          | NVIDIA GB200 NVL72 [40, 41]                | UpDown                    |

|------------------------|--------------------------------------------|--------------------------------------------|---------------------------|

| Compute Engines        | 1 Grace CPU                                | 1 Grace CPU                                | 1 CPU                     |

|                        | 1 Hopper H200 NVL GPU                      | 2 Blackwell B200 GPU                       | 2048 UpDown Lanes         |

| Node CPU cores         | 72 @3.1GHz                                 | 72 @3.1GHz                                 |                           |

| Node GPU SMs/          | 132 @1365 MHz                              | 528 @1665 MHz                              | 32 @2GHz                  |

| UpDown Accelerators    |                                            |                                            |                           |

| Peak FP64 Perf         | 30 TFLOPS                                  | 90 TFLOPS                                  | 4.1 TFLOPS                |

| Node Memory            | 144GB HBM3e(GPU)                           | 384GB HBM3e(GPU)                           | 512GB HBM3e               |

|                        | 96GB HBM3(GPU)                             | 480GB LPDDR5X(CPU)                         |                           |

|                        | 480GB LPDDR5X(CPU)                         |                                            |                           |

| Node Memory            | $4.9~\mathrm{TB/s~HBM3e(GPU)}$             | 16 TB/s HBM3e(GPU)                         | $9.6~\mathrm{TB/s~HBM3e}$ |

| Bandwidth              | 4TB/s HBM3(GPU)                            | $0.5 \mathrm{TB/s}\ \mathrm{LPDDR5X(CPU)}$ |                           |

|                        | $0.5 \mathrm{TB/s}\ \mathrm{LPDDR5X(CPU)}$ |                                            |                           |

| Network Types          | NVLink                                     | NVLink                                     |                           |

| Node Ports             | 18                                         | 36                                         |                           |

| Node GPU Injection     | $450~\mathrm{GB/s}$                        | $1.8~\mathrm{TB/s}$                        | $6.4~\mathrm{TB/s}$       |

| ${f Bandwidth}$        |                                            |                                            | (assume)                  |

| ${\bf Network/Memory}$ | 4.94%                                      | 11.25%                                     | 66.7%                     |

| ${f Bandwidth}$        |                                            |                                            |                           |

| Network Traffic        | 15 B                                       | 20 B                                       | 1561 B                    |

| Per 1k FP64            |                                            |                                            |                           |

| Nodes                  | 256                                        | 36                                         | 16,384                    |

| CPU cores              | 18,432 @3.1GHz                             | 2,592 @3.1GHz                              |                           |

| GPU SMs/Accs           | 33,792 @1365 MHz                           | 19,008 @1665 MHz                           | 524,288 @2 GHz            |

| Peak FP64 Perf         | 7.68 PFLOPS                                | 3.24 PFLOPS                                | 67.11 PFLOPS              |

| System Memory          | 36TB HBM3e(GPU)                            | 13.5TB HBM3e(GPU)                          | 8PB HBM3e                 |

|                        | 24TB HBM3(GPU)                             | 17PB LPDDR5X(CPU)                          |                           |

|                        | 120TB LPDDR5X(CPU)                         |                                            |                           |

| System Ports           | 4608                                       | 1296                                       |                           |

| System GPU Injection   | $112.5~\mathrm{TB/s}$                      | $65~\mathrm{TB/s}$                         | $102.4~\mathrm{PB/s}$     |

| ${\bf Bandwidth}$      |                                            |                                            |                           |

| System Bisection       | $56.25~\mathrm{TB/s}$                      | $32.5~\mathrm{TB/s}$                       | $51.2~\mathrm{PB/s}$      |

| Bandwidth              |                                            |                                            |                           |

| Network Topology       | 2-level Fat Tree                           | 1-level Fat Tree                           |                           |

| Network Switch         | NVLink 4 Switch                            | NVLink 5 Switch                            |                           |

| Power                  | 256 KW                                     | 86 KW                                      | 9.64 MW                   |

| BFS GTEPS              |                                            |                                            | 935,000                   |

## CHAPTER 3

## **UPDOWN SYSTEM**

UpDown [42, 43, 44, 45, 46] is a large-scale parallel system design initiative funded under IARPA's Advanced Graphic Intelligence Logical Computing Environment (AGILE) program [47]. The overall objective of the program is to achieve breakthrough performance on irregular applications and graphs characterized by extreme skew and low data reuse.

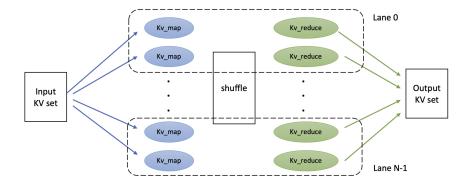

In this chapter, we first provide an overview of the UpDown design, highlighting its unique architectural features that are critical for the subsequent network performance analysis. We then extend the discussion from a single-node design to a multi-node system and introduce the UpDown network packet format. Next, we briefly introduce the UDKVMSR [44] (UpDown Key-Value pair Map Shuffle Reduce) framework, which is used for graph application mapping, along with the implementations of Triangle Counting (TC), Breadth-First Search (BFS), and PageRank (PR) built on UDKVMSR. Finally, we describe Fastsim2, a cycle-accurate, fast, multi-threaded simulator capable of simulating up to 256 UpDown nodes efficiently.

# 3.1 UpDown Architecture

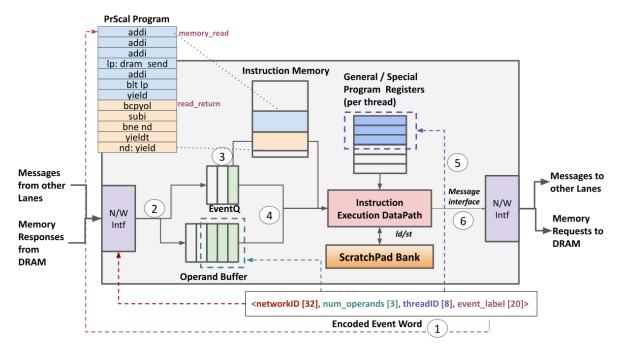

The UpDown system is composed of multiple UpDown nodes, where each node consists of one CPU, 32 UpDown accelerators, and 8 HBM3e DRAM stacks, as illustrated in Figure 3.1. Each UpDown accelerator is positioned between the CPU and the DRAM, enabling both the CPU and the UpDown accelerators to directly access the memory. An individual UpDown accelerator contains 64 event-driven programmable lanes, with each lane equipped with a 64 KB software-controlled scratchpad memory. These lanes are capable of generating unlimited event messages and issuing direct DRAM accesses.

Events are first-class primitives in the UpDown ISA, represented using event-words, which

Figure 3.1: UpDown Node has 1 CPU, 32 UpDown accelerators with uniform access to 8 HBM stacks. Each UpDown accelerator has 64 event-driven programmable lanes.

combine traditional hardware events such as DRAM\_load and DRAM\_load\_ack and custom software-defined events under a unified programmable event framework. As illustrated in Figure 3.2, an *event-word* encodes the following information: compute name (event\_label, 20 bits), thread ID (8 bits), compute location (network ID, 32 bits), and message size (num\_operands, 3 bits). Both software and hardware events are captured through this unified interface and managed using specific ISA instructions [42], as summarized in Table 3.1. These event messages facilitate communication between UpDown lanes and the

#### DRAM.

Figure 3.2: Event Driven Execution on UpDown lane

Table 3.1: UpDown Instruction Set Architecture Highlights

| Category                              | Execution Mechanisms and Instructions                                                                                                                                                            |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-latency non-blocking thread/event | Thread spawn/invoke: Msg arrival event, send msg; Thread yield/destroy: (yield, yieldt); Register naming for Msg Operands, use in add-class, send, and load-store (scratchpad memory) operations |

| Split-transaction DRAM                | DRAM send instructions (sendm, sendmops, sendmr); DRAM responses come to software-defined event label                                                                                            |

| Messaging (incl DRAM)                 | Single instruction sends of 1-8 words: send, sendr, sendops, sendm (DRAM), sendmops (DRAM)                                                                                                       |

Specifically, the send instruction carries an event\_word, a continuation\_word, and a payload of up to nine data words (one word = 8B). Using the send instruction, a new thread (with threadID 0xFF) can be launched on a specified lane (designated by networkID) to execute from a given event\_label, all encoded within the event\_word. The continuation\_word specifies continuation-passing information using the same encoding format. DRAM accesses, performed using the sendm instruction, follow similar semantics; however, the event\_word is replaced by a physical memory address, while the continuation word

specifies the event\_label for response synchronization. The details of event\_word, physical DRAM address, and networkID encoding are summarized in Table 3.2.

Table 3.2: Event Word and Address Encoding

| Event Word (64 bits)       |           |                                                         |  |  |

|----------------------------|-----------|---------------------------------------------------------|--|--|

| Name                       | Bit Field | Description                                             |  |  |

| networkID                  | [63:32]   | Lane identifier where the event should be sent.         |  |  |

| threadID                   | [31:24]   | Thread ID to be activated in the lane. A value of 0xFF  |  |  |

|                            |           | creates a new thread.                                   |  |  |

| thread_mode                | [23]      | Defines the register map to be used (regular/streaming  |  |  |

|                            |           | mode).                                                  |  |  |

| num_ops                    | [22:20]   | Number of operands in the current event.                |  |  |

| event_label                | [19:0]    | Address offset of the instruction block to be executed. |  |  |

| Physical Address (64 bits) |           |                                                         |  |  |

| Name                       | Bit Field | Description                                             |  |  |

| reserved                   | [63:60]   | Reserved bits.                                          |  |  |

| nodeID                     | [59:45]   | Node identifier associated with the address.            |  |  |

| physical_addr              | [44:0]    | Physical DRAM address.                                  |  |  |

| NetworkID (32 bits)        |           |                                                         |  |  |

| Name                       | Bit Field | Description                                             |  |  |

| top/ud                     | [31]      | Always 0 to indicate UpDown Accelerator networkID.      |  |  |

| reserved                   | [30]      | Reserved bit.                                           |  |  |

| send_policy                | [29:27]   | Policy for dynamic management of message targets.       |  |  |

| NID                        | [26:11]   | Node ID.                                                |  |  |

| UDID                       | [10:6]    | Accelerator ID.                                         |  |  |

| LID                        | [5:0]     | Lane ID.                                                |  |  |

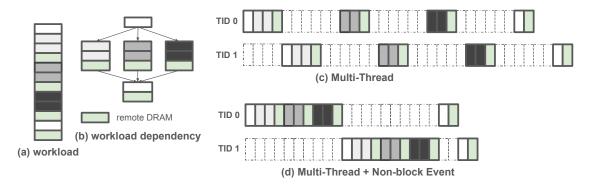

Due to previous unique architecture features, UpDown include the following key features that generate short event message with low overhead:

- Low Latency Event / Thread: hardware event queues, hardware event-driven thread scheduling, hardware-supported thread create; schedule; terminate.

- Short Message: Direct ISA messaging for 1-8 words operands by registers with 2 event words for destination and continuation.

- Non-blocking Event Scheduler: Each DRAM access send one to eight-word load/store

operations to DRAM, asynchronous return and trigger another event by continuation

word. So there is no blocking inside event.

• Flexible Programmability: An instruction set that realizes customized and general computation efficiently

# 3.2 UpDown System

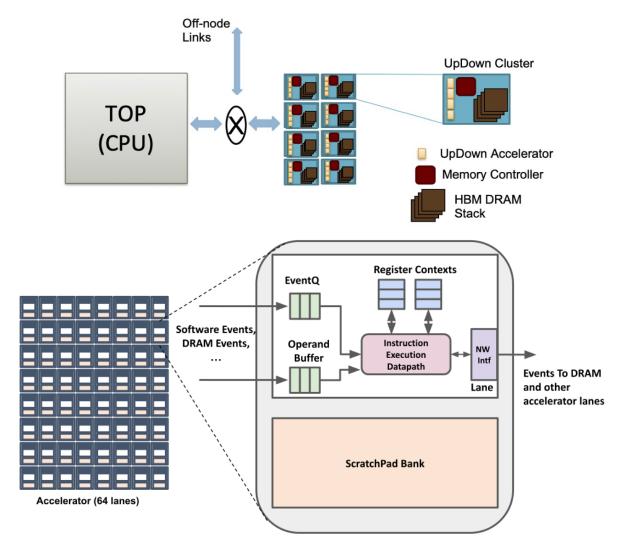

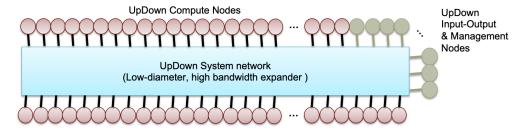

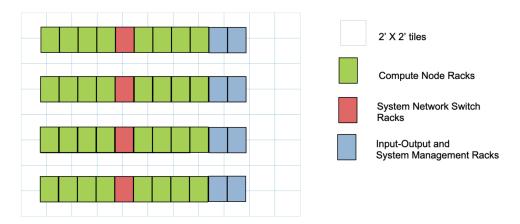

The UpDown system consists of a compute array comprising 16,384 UpDown nodes, along with a separate set of input/output (I/O) nodes responsible for external networking and storage. The compute array is organized into 32 racks, with each rack housing 512 nodes. In addition to the compute racks, there are 8 I/O and system management racks, containing a total of 28 I/O nodes.

In this paper, we focus exclusively on the compute array and its internal system network. Memory within an UpDown node is divided into local memory and global memory. Local memory is accessible only by the node itself, whereas global memory is shared across the entire UpDown system. Consequently, there are two types of network messages: computation messages, where a lane sends an event to a remote lane, and remote global memory accesses, where a node accesses shared global memory residing on a remote node.

Figure 3.3: UpDown System consists of a compute array (16,384 UpDown nodes) and a separate set of input/output nodes that connect external networking and storage.

# 3.3 UpDown System Network Design

UpDown accelerators and TOP CPUs can send messages directly to the system network, as illustrated in the node diagram (Figure 3.2), and can also receive incoming messages from the